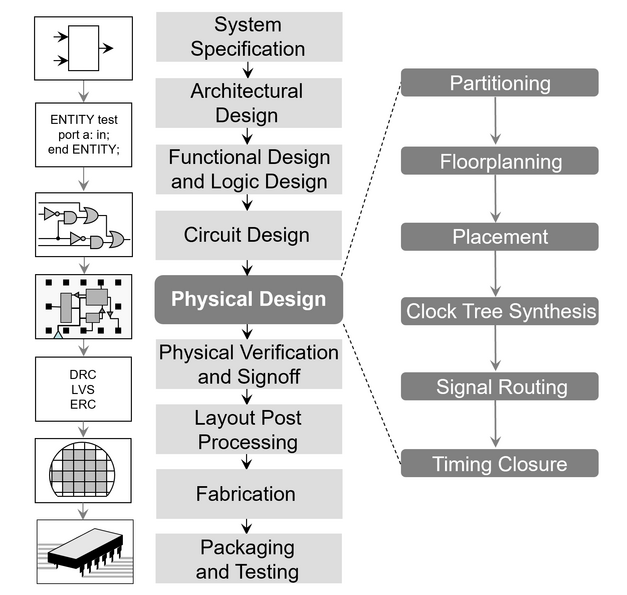

physical design is a step in the standard design cycle which follows after the circuit design. At this step, circuit representations of the components (devices and interconnects) of the design are converted into geometric representations of shapes which, when manufactured in the corresponding layers of materials, will ensure the required functioning of the components. This geometric representation is called integrated circuit layout. This step is usually split into several sub-steps, which include both design and verification and validation of the layout

Modern day Integrated Circuit (IC) design is split up into Front-end design using HDL's, Verification and Back-end Design or Physical Design. The next step after Physical Design is the Manufacturing process or Fabrication Process that is done in the Wafer Fabrication Houses. Fab-houses fabricate designs onto silicon dies which are then packaged into ICs.

The main steps in the ASIC physical design flow are:

- Design Netlist (after synthesis)

- Floorplanning

- Partitioning

- Placement

- Clock-tree Synthesis (CTS)

- Routing

- Physical Verification

- GDS II Generation

These steps are just the basic. There are detailed PD flows that are used depending on the Tools used and the methodology/technology. Some of the tools/software used in the back-end design are :

- Cadence (SOC Encounter, VoltageStorm, NanoRoute)

- Synopsys (Design Compiler, IC Compiler)

- Magma (BlastFusion, etc.)

- Mentor Graphics (Olympus SoC, IC-Station, Calibre)

A more detailed Physical Design Flow is shown below.

No comments:

Post a Comment